半导体测试:

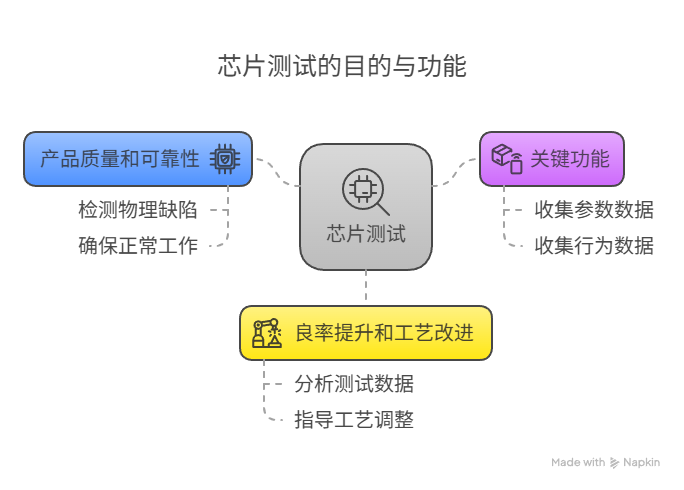

半导体制造流程包含晶圆制造–>测试–>封装等,这是一个互联和在不断发展的半导体生态系统。半导体测试在整个集成电路价值链中扮演着至关重要的角色,包括以下几点:

1.确保产品质量和可靠性:测试的首要目的是确保制造出来的芯片符合设计规范并能正常工作,它可以检测出芯片中存在的各种物理缺陷,例如开路、短路、桥接或栅氧化层击穿等。

2.关键功能在于连接产品并收集信息:测试不仅仅是简单的通过/失败判定,它还收集大量的参数和行为数据。例如,参数测试可以衡量芯片在额定电压下的工作频率或静态功耗。

3.促进良率提升和工艺改进:通过分析测试数据,可以发现制造过程中的系统性问题或随机缺陷,从而指导工艺工程师进行调整和优化,提高产品的良率。

WAT定义:

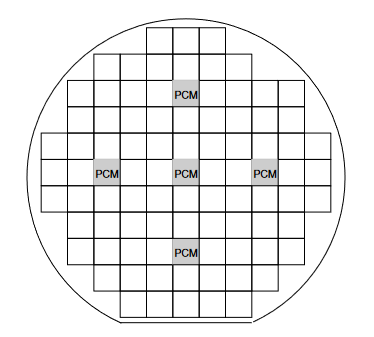

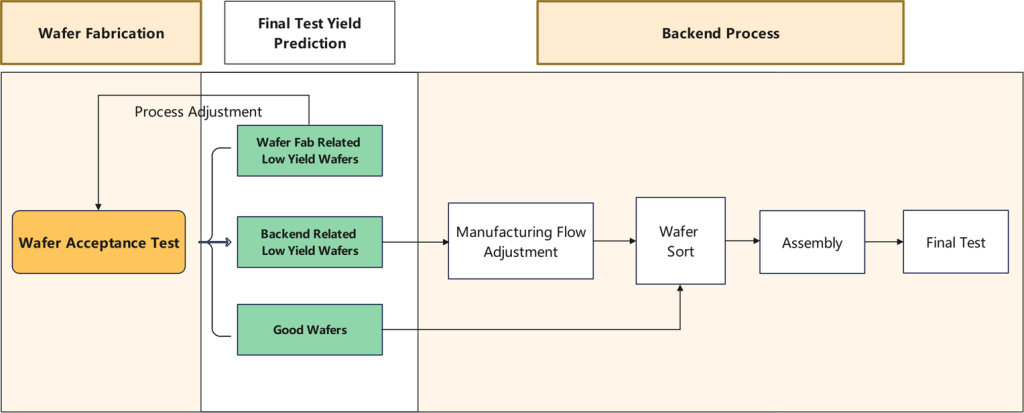

WAT(Wafer Acceptance Test)是在晶圆制造过程中进行的测试,位于所有加工工艺之后,出货品质检测之前,又称为工艺控制监测—PCM(Process Control Monitor)。通过在晶圆各个特定位置上测量微观器件的电性能,验证工艺步骤的完成质量和工艺参数的稳定性。他们也是FAB厂作为SPC(Statistical Process Control,统计过程控制)的一部分,用于表征和控制制程技术。

WAT结构说明:

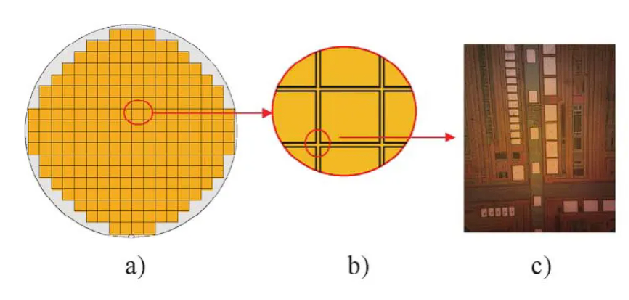

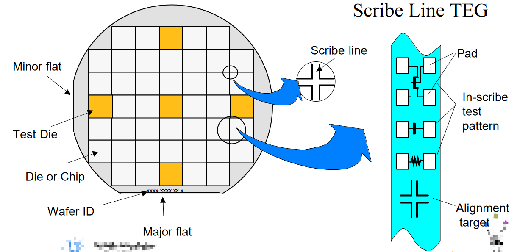

如图所示为划片槽中的WAT测试结构,划片槽是沿着晶圆边缘的窄条,用于后续的切割(dicing)过程。图a是整块晶圆产品上的芯片,每一个小格子代表一颗芯片;图b是放大后的图形,可以看到芯片间的划片槽;图c是显微镜下的芯片划片槽,白色的方块区域是顶层金属窗口,通常称为封装金属窗口(Bonding PAD),WAT测试结构在PAD与PAD之间,很多不同的测试结构组成一组测试模组,芯片代工厂会给每组测试模组定义一个名称,每一片晶圆会包含很多这样的不同的WAT测试模组。

通过对DIE与DIE之间的划片槽( Scribe Line )的测试键( Testkey )上的测试,利用电性参数来监控各步的工艺是否稳定,然后生成一个测试通过与否的报表。

WAT测试结构并不是设计在实际产品芯片内部的(会增加成本),Scribe Line的宽度60~150μm之间,其中会有bonding pad,WAT测试结构在PAD与PAD之间,很多不同的Testkeys组成一组测试模组。

我们为什么要用WAT?

核心目标:确保晶圆在封装和切割前,它的电气特性和工艺参数符合设计标准;从而为后续工艺步骤提供质量保障和性能支持。总的来说就是三点:验证制造的晶圆是否符合规范、表征器件的电学特性、支持工艺开发和调试。

WAT的测试Rule:

1.WAT对每一片wafer进行测试,一般一个Lot(晶圆批次)会有25片wafer;

2.WAT测试会在每片wafer上选取x个点(一般奇数个,覆盖到整个晶圆)用于代表整片wafer水平;

3.WAT测试在每个点上必需测所有关键的参数WAT key Items;